Презентація на тему:

Типи процесорів та їх використання у ВКС.

Завантажити презентацію

Типи процесорів та їх використання у ВКС.

Завантажити презентаціюПрезентація по слайдам:

Тема 4. Типи процесорів та їх використання у ВКС. Викладач: д.т.н., проф. Саченко А.О. Високопродуктивні комп’ютерні системи Тернопіль 2006 Тернопільський Національний Економічний Університет Факультет комп'ютерних інформаційних технологій Кафедра Інформаційно обчислювальних систем та управління

Зміст лекції 1. CISC процесори. 2. RISC процесори. 3. MISC процесори. 4. Матричні процесори. 5. Процесори з конвейєрною обробкою. 6. Суперскалярний процесор. 7. VLIW машини. 8. Комунікаційний процесор.

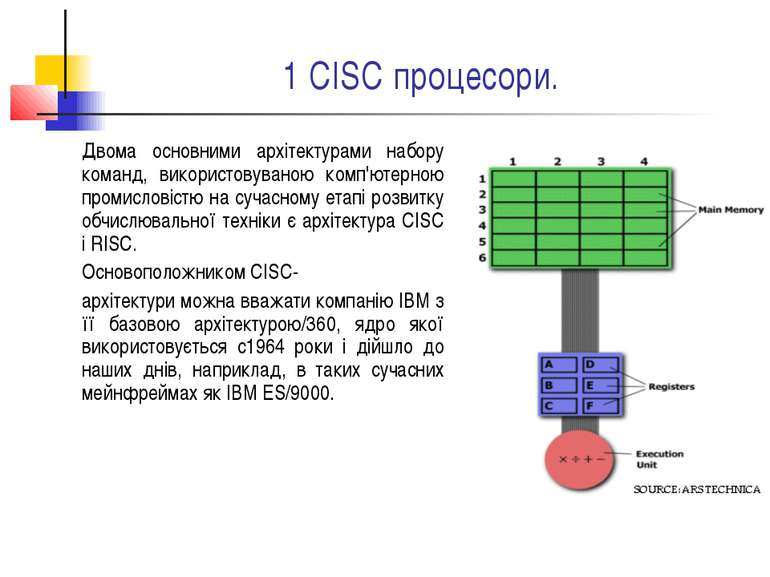

1 CISC процесори. Двома основними архітектурами набору команд, використовуваною комп'ютерною промисловістю на сучасному етапі розвитку обчислювальної техніки є архітектура CISC і RISC. Основоположником CISC- архітектури можна вважати компанію IBM з її базовою архітектурою/360, ядро якої використовується с1964 роки і дійшло до наших днів, наприклад, в таких сучасних мейнфреймах як IBM ES/9000.

Ця архітектура є практичним стандартом для ринку мікрокомп'ютерів. Для CISC-процесорів характерний: порівняльне невелике число регістрів загального призначення; велика кількість машинних команд, деякі з яких навантажені семантично аналогічно операторам високорівневих мов програмування і виконуються за багато тактів; велика кількість методів адресації; велика кількість форматів команд різної розрядності; переважання двоадресного формату команд; наявність команд обробки типу регістр-пам'ять.

2. RISC процесори. Основою архітектури сучасних робочих станцій і серверів є архітектура комп'ютера з скороченим набором команд (RISC - Reduced Instruction Set Computer). Зачатки цієї архітектури йдуть своїм корінням до комп'ютерів CDC6600, розробники яких (Торнтон, Крей і ін.) усвідомили важливість спрощення набору команд для побудови швидких обчислювальних машин.

Цю традицію спрощення архітектури С. Крэй з успіхом застосував при створенні широко відомої серії суперкомп'ютерів компанії Cray Research. Проте остаточне поняття RISC в сучасному його розумінні сформувалося на базі трьох дослідницьких проектів комп'ютерів: процесора 801 компанії IBM, процесора RISC університету Берклі і процесора MIPS Стенфордського університету.

3. MISC процесори. MISC- принцип "простоти", початковий для RISC процесорів, дуже швидко відійшов на задній план. У запалі боротьби за максимальну швидкодію, RISC наздогнав і перегнав багато CISC процесори по складності.

Тим часом очевидні багато проблем RISC архітектури : RISC команди все ще повільні. Використовується багатоступінчатий конвейєр для їх виконання. Проте всякий раз при галуженні програми конвейєр скидається і заповнюється наново. Із збільшенням швидкодії росте розрив між швидким процесором і повільною пам'яттю. Для збільшення швидкості доступу до пам'яті необхідно використовувати кеш пам'ять RISC процесори дуже неефективні на операціях виклику і повернення підпрограм.

4 Матричні процесори. Матричний процесор об'єднує безліч фунцкціональних пристроїв, що логічно об'єднаних в матрицю і працюють в SIMD-стилі. Векторний же процесор має вбудовані інструкції для обробки векторів даних, що дозволяє ефективно завантажити конвейєр з функціональних пристроїв.

Організація систем подібного типу на перший погляд достатньо проста. Вони мають загальний пристрій, що управляє, генерує потік команд і велике число процесорних елементів, що працюють паралельно і оброблювальних кожна свій потік даних. Таким чином, продуктивність системи виявляється рівній сумі проїзводітельностей всіх процесорних елементів. Саме характер зв'язків між процесорними елементами і визначає різні властивості системи.

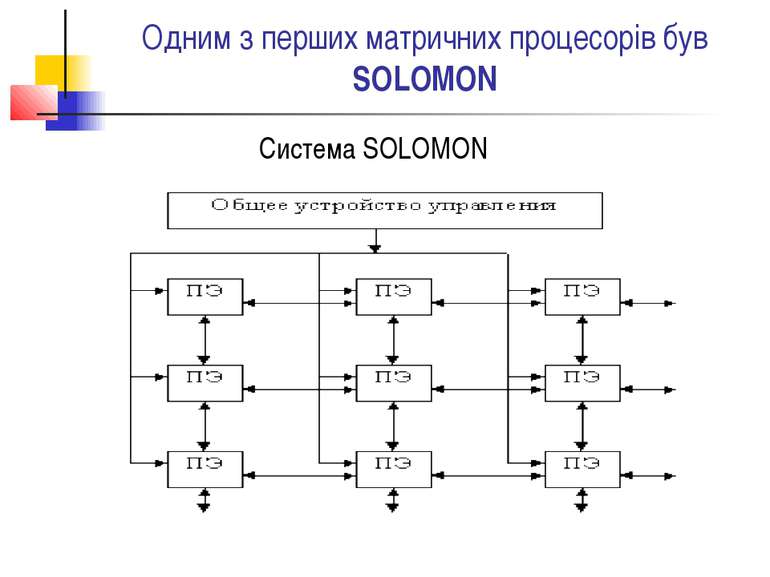

Система SОLOМОN містить 1024 процесорних елементу, сполучені у вигляді матриці: 32х32. Кожен процесорний елемент матриці включає процесор, що забезпечує виконання послідовних порозрядних арифметичних і логічних операцій, а також оперативне ЗУ, місткістю 16 Кбайт. Довжина слова - змінна від 1 до 128 розрядів. У процесорному елементі використовується, багато модальна логіка, яка дозволяє кожному процесорному елементу виконувати або не виконувати загальну операцію залежно від значень оброблюваних даних.

5.Процесори з конвейєрною обробкою. Розробники архітектури комп'ютерів відвіку вдавалися до методів проектування, відомих під загальною назвою "Поєднання операцій", при якій апаратура комп'ютера у будь-який момент часу виконує одночасно більш за одну базову операцію. Цей загальний метод включає два поняття: паралелізм і конвейєризацію. Конвейєризація (або конвейєрна обробка) в загальному випадку заснована на розділенні що підлягає виконання функції на дрібніші частини, звані ступенями, і виділенні для кожної з них окремого блоку апаратури.

Так обробку будь-якої машинної команди можна розділити на декілька етапів (декілька ступенів), організувавши передачу даних від одного етапу до наступного. При цьому конвейєрну обробку можна використовувати для поєднання етапів виконання різних команд. Продуктивність при цьому зростає завдяки тому, що одночасно на різних ступенях конвейєра виконуються декілька команд. Конвейєрна обробка такого роду широко застосовується у всіх сучасних швидкодіючих процесорах.

6.Суперскалярний процесор Існують два типи машин з паралельною видачею декількох команд в кожному такті: Суперскалярні машини; VLIW-машини (машини з дуже довгим командним словом)

Суперскалярні машини можуть видавати на виконання в кожному такті змінне число команд, і робота їх конвейєрів може плануватися як статично за допомогою компілятора, так і за допомогою апаратних засобів динамічної оптимізації. На відміну від суперскалярних машин, VLIW-машини видають на виконання фіксовану кількість команд, які сформатовані або як одна велика команда, або як пакет команд фіксованого формату.

Суперскалярні машини використовують паралелізм на рівні команд шляхом посилки декількох команд із звичайного потоку команд в декілька функціональних пристроїв. Додатково, щоб зняти обмеження послідовного виконання команд, ці машини використовують механізми позачергової видачі і позачергового завершення команд, прогнозування переходів, кеші цільових адрес переходів і умовне (по припущенню) виконання команд. Збільшена складність, що реалізовується цими механізмами, створює також проблеми реалізації точного переривання.

7.VLIW машини. Архітектура ж машин з дуже довгим командним словом (VLIW Very - Long Instruction Word) дозволяє скоротити об'єм устаткування, потрібного для реалізації паралельної видачі декількох команд

Більша кількість команд видається паралельно, тим більше ця економія : більша кількість команд видається паралельно, тим більше ця економія двохпотокова суперскалярна організація, що допускає паралельне виконання пари простих команд; наявність двох незалежних двохканальних асоціативних для множини кешів для команд і для даних, що забезпечують вибірку даних для двох операцій в кожному такті; динамічне прогнозування переходів; конвейєрна організація пристрою плаваючої крапки з 8 ступенями; двійкова сумісність з існуючими процесорами сімейства 80x86.

Перш за все нова мікроархітектура цього процесора базується на ідеї суперскалярної обробки (правда з деякими обмеженнями). Основні команди розподіляються по двох незалежних виконавчих пристроях (конвейєрам U і V). Конвейєр U може виконувати будь-які команди сімейства x86, включаючи цілочисельні команди і команди з плаваючою крапкою. Конвейєр V призначений для виконання простих цілочисельних команд і деяких команд з плаваючою крапкою.

8.Комунікаційний процесор. Комунікаційний процесор цілком виділяється для обробки передаваної інформації, контролю і усунення помилок, кодування повідомлень, управління лінією зв'язку і т.п.) У окремі класи слід виділити: систолічні процесори нейросигнальні процесори.

Систолічні процесори Процесори (процесорні матриці) систол - це чіпи, як правило, близькі до звичайних RISC-процесорів і об'єднуючі в своєму складі деяке число процесорних елементів. Решта всієї ж логіки, як правило, повинна бути реалізована на базі периферійних схем.

Нейросигнальні процесори У нейросигнальних процесорів ядро є типовий сигнальний процесор, а реалізована на крістале додаткова логіка забезпечує виконання нейросетевих операцій (наприклад, додатковий векторний процесор і т.п.).

Схожі презентації

Категорії